Polliwog PollEx PCB Signal Integrity

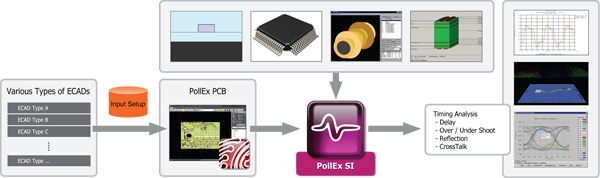

相关常见问题PollEx SI (Signal Integrity)是一个快速,准确,易于使用的信号完整性验证程序,用于分析PCB设计。它允许用户在设计阶段检测和纠正信号完整性问题,从而消除或显著减少昂贵的设计迭代。

特征

- 信号完整性验证功能与PollEx PCB紧密集成,并与各种PCB设计工具接口。

- 在整个PCB设计阶段提供完整的信号完整性解决方案,包括预设计和后布局阶段。

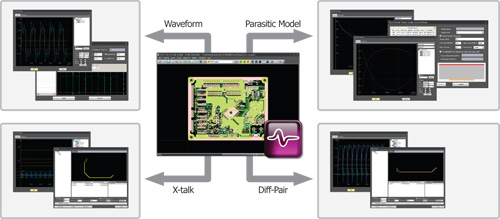

- 时域分析功能包括波传播延迟,反射,串话干扰和眼图分析。

- 频域分析能力包括散射,导纳和阻抗参数矩阵的计算。

- 全自动内置分析功能包括层叠加优化,网络拓扑分析和后路由信号完整性验证。

- 晶体管级SPICE模型和行为型SPICE和IBIS模型都可用于驱动器/接收器/终端器件模型。

- 各种IC封装管脚寄生模型,如集中式RLC,分布式RLC,SPICE网表和S参数可用于信号完整性分析。

- 内置Polliwog SPICE用于精确模拟。

- 内置电磁积分方程求解器使用矩量法计算耦合的有损耗色散传输线的准确的频率相关的RLCG矩阵,并使用网络合成方法产生等效的宽带SPICE网络表。

- 内置三维电动有限元求解器提取耦合通孔的S参数,并使用网络合成方法生成等效宽带SPICE网络表。

- 内置零件和材料编辑器,允许用户轻松生成I / O缓冲区模型,封装寄生模型和材料数据,并构建部件和材料库以供重复使用。

- 自动识别复合网络,并且连接无源器件可以被建模为用于复合网络分析的RLC,SPICE网络表和S参数。

- 自动识别差分网对,并对差分对执行分析。

- 可以为第三方EM求解器和电源完整性分析工具生成输入数据文件。

- PollEx SI模块已设计为由多个工程学科共同使用,以便设计项目成员可以在整个设计过程中快速验证设计和设计更改。

主要优点

- 无需在PCB设计和信号完整性分析工具之间进行接口或数据传输。

- 无需购买和维护昂贵的独立的信号完整性工具。

- Signal integrity 专家可以监督更多的设计,因为大多数内置的信号完整性验证功能可以被电气工程师,PCB设计师和制造工程师有效地使用。

- 设计项目成员之间的密切协作允许在缩短的设计时间内的有更好的设计。

京ICP备09015132号-996 | 网络文化经营许可证京网文[2017]4225-497号 | 违法和不良信息举报电话:4006561155

© Copyright 2000-2025 北京哲想软件有限公司版权所有 | 地址:北京市海淀区西三环北路50号豪柏大厦C2座11层1105室